P2 Data Logger : Différence entre versions

(→Caracteristiques SPARTAN 6 XILINX LX45) |

(→Caractéristiques du TE0603) |

||

| Ligne 103 : | Ligne 103 : | ||

*5 Header connectors with up to 114 user IOs | *5 Header connectors with up to 114 user IOs | ||

*2 Push-buttons for reset and user function | *2 Push-buttons for reset and user function | ||

| − | [http://www.trenz-electronic.de/fileadmin/docs/Trenz_Electronic/TE0600-GigaBee_series/TE0603/documents/UM-TE0603.pdf Datasheet TE0603] | + | [http://www.trenz-electronic.de/fileadmin/docs/Trenz_Electronic/TE0600-GigaBee_series/TE0603/documents/UM-TE0603.pdf Datasheet TE0603] <br><br><br><br> |

===Semaine 3 (05/10/2015)=== | ===Semaine 3 (05/10/2015)=== | ||

Version du 12 octobre 2015 à 10:49

Sommaire

- 1 Cahier des charges

- 2 Suivi de l'avancement du Projet

- 2.1 Semaine 1 (21/09/2015)

- 2.2 Semaine 2 (28/09/2015)

- 2.3 Semaine 3 (05/10/2015)

- 2.4 Semaine 4 (12/10/2015)

- 2.5 Semaine 5 (19/10/2015)

- 2.6 Semaine 6 (26/10/2015)

- 2.7 Semaine 7 (02/11/2015)

- 2.8 Semaine 8 (09/11/2015)

- 2.9 Semaine 9 (16/11/2015)

- 2.10 Semaine 10 (23/11/2015)

- 2.11 Semaine 11 (30/11/2015)

- 2.12 Semaine 12 (07/12/2015)

- 2.13 Semaine 13 (14/12/2015)

- 2.14 Semaine 14 (04/01/2016)

- 2.15 Semaine 15 (11/01/2016)

- 2.16 Semaine 16 (18/01/2016)

- 2.17 Semaine 17 (25/01/2016)

- 2.18 Semaine 18 (01/02/2016)

- 2.19 Semaine 19 (08/02/2016)

- 2.20 Semaine 20 (15/02/2016)

- 2.21 Semaine 21 (22/02/2016)

Cahier des charges

Présentation générale du projet

Dénomination du sujet par les enseignants

| Objectif | Réaliser une plate-forme de mesure de la consommation d'équipement électroniques |

|---|---|

| Description | La consommation des équipements électroniques est devenue un enjeu majeur puisque les équipements sont très souvent utilisés en situation de mobilité. La réduction de la consommation passe par la compréhension des sources de consommation que ce soit par le logiciel ou par le matériel.

Afin de comprendre les mécanismes de consommation, il est nécessaire de pouvoir mesurer le courant des différents composants d'un système. Dans ce projet, nous proposons la réalisation d'une plate-forme permettant la mesure de courant. Cette plate-forme devra être ouverte et facilement reconfigurable (ajout / retrait de voies de mesures, filtrage des mesures, ...) La plate-forme sera constituée de :

|

Contexte

Dans le cadre d'une réalisation de projet de fin d'étude, on se propose de réaliser un "data logger". Durant les semaines à venir, je vais travailler sur un dispositif qui stockera des données numériques envoyé depuis un convertisseur analogique numérique dans une barrette de RAM avant de les rendre accessible par une liaison RS232. Le but de se projet est de compléter le panel de technologie disponible pour un laboratoire qui possède une...

Objectif du projet

- stocker en RAM une série de donnée le plus rapidement possible

- construire interface permettant de recuperer les infomations via un RJ45 protocole Ethernet

- rendre modulaire le code en permettant de modifier facilement de la taille des mots d'entrée (passer de 8 bits à 10 puis 16 ...)

- rendre modulaire le code en permettant d'ajouter un fréquencemètre

- développer une carte support pour le LX45 maitriser les temps de propagations des signaux sur le typon, en direction de la barrette de RAM

Description du projet

Choix techniques : matériel, logiciels, sources

- Plateforme SPARTAN 6 (lx45) chez TRENDS Electronic TE0603

- OPENCORES.ORG

- Caracteristiques du LX45

- Tutoriel XILINX ISE webpack

Étapes du projet

Sources

Fiche commerciale

Sous la main:

à voir

Suivi de l'avancement du Projet

Semaine 1 (21/09/2015)

- Étude du cahier des charges.

- Réunion avec les enseignants responsables.

- Présentation du sujet.

- Création du wiki.

Semaine 2 (28/09/2015)

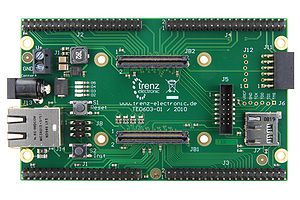

La board que m'ont fournie les encadrants se compose se compose d'une carte mère et d'une carte support. La carte mère, nommé TE0600 est composé d'un FPGA Xilinx SPARTAN 6 LX45. C'est le "cerveau" du projet qui vient se brancher sur une carte support qui me servira au développement (programmation, IOs, carte mémoire, alimentation, Ethernet...). Celle ci se nomme TE0603. Elles seront indissociable pendant toute la période de développement.

- Recherche approfondis sur le FPGA:

Caracteristiques SPARTAN 6 XILINX LX45

- consommation: 0.6A

- 45nm low power process technology with 6-input LUTs

- 1080MHz clock management tiles (2 DCM + 1 PLL)

- 320MHz Block RAM from 216 - 4824 Kbits

- Memory interface controllers blocks from 0 - 4

- 1.08Gbps SelectIO™ technology

- 390MHz DSP48A1 slices from 8 - 180

- Embedded processing

Spartan-6 FPGA Electrical Characteristics

Commerciale presentation

General Description

Caractéristiques de TE0600

Industrial-grade Xilinx Spartan-6 LX FPGA micromodule (LX45 / LX100 / LX150)

- 10/100/1000 tri-speed Gigabit Ethernet transceiver (PHY)

- 2 x 16-bit-wide 1 Gb (128 MB) or 4Gb (512 MB) DDR3 SDRAM

- 128Mb (16 MB) SPI Flash memory (for configuration and operation)accessible through:

- 1Kb Protected 1-Wire EEPROM with SHA-1 Engine

- JTAG port (SPI indirect)

- FPGA configuration through:

- B2B connector

- JTAG port

- SPI Flash memory

- Plug-on module with 2 × 100-pin high-speed hermaphroditic strips

- Up to 52 differential, up to 109 single-ended (+ 1 dual-purpose) FPGA I/O pins available on B2B strips

- 4.0 A x 1.2 V power rail

- 1.5 A x 1.5 V power rail

- 125 MHz reference clock signal

- Single-ended custom oscillator (option)

- eFUSE bit-stream encryption (LX100 or larger)

- 1 user LED

- Evenly-spread supply pins for good signal integrity

- Other assembly options for cost or performance optimization available upon request.

Caractéristiques du TE0603

- Board power supply via screw terminals, DC jack

- JTAG header compatible with Xilinx parallel cable III, IV and USB cable HW-USB

- Small form factor: 115x70 mm

- Micro SD connector

- 5 Header connectors with up to 114 user IOs

- 2 Push-buttons for reset and user function