P2 Data Logger : Différence entre versions

(→Objectif du projet) |

|||

| (190 révisions intermédiaires par un autre utilisateur non affichées) | |||

| Ligne 1 : | Ligne 1 : | ||

| + | <include nopre noesc src="/home/pedago/pimasc/include/video-DataLogger-iframe.html" /> | ||

| + | __TOC__ | ||

| + | <br style="clear: both;"/> | ||

==Cahier des charges== | ==Cahier des charges== | ||

===Présentation générale du projet=== | ===Présentation générale du projet=== | ||

| Ligne 32 : | Ligne 35 : | ||

*développer une carte support pour le LX45 maitriser les temps de propagations des signaux sur le typon, en direction de la barrette de RAM | *développer une carte support pour le LX45 maitriser les temps de propagations des signaux sur le typon, en direction de la barrette de RAM | ||

| − | ====Description du | + | ===Étapes du projet=== |

| − | ==== | + | Le projet va se dérouler en plusieurs étapes.<br> |

| + | 1)Etude des plates-formes de programmation | ||

| + | <br> | ||

| + | 2)Etude de la problématique | ||

| + | <br> | ||

| + | 3)Proposition de solutions et argumentaire | ||

| + | |||

| + | ===Choix techniques : matériel, logiciels, sources=== | ||

| + | *[http://www.opencores.org OPENCORES.ORG] | ||

| + | *[http://www.ztex.de/usb-fpga-1/usb-fpga-1.15.e.html Caracteristiques du LX45] | ||

| + | *[http://www.xilinx.com/itp/xilinx10/isehelp/ise_c_overview.htm Logiciel XILINX ISE ] (overview) | ||

| + | |||

| + | ==Suivi des étapes du Projet== | ||

| + | ===Etude des plates-formes de programmation=== | ||

| + | ====TE0600 & TE0603==== | ||

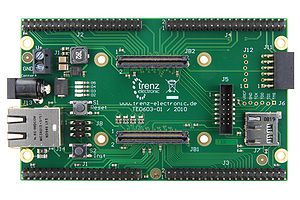

| + | La board que m'ont fournie les encadrants se compose se compose d'une carte mère et d'une carte support. La carte mère, nommé TE0600 est composé d'un FPGA Xilinx SPARTAN 6 LX45. C'est le "cerveau" du projet qui vient se brancher sur une carte support qui me servira au développement (programmation, IOs, carte mémoire, alimentation, Ethernet...). Celle ci se nomme TE0603. Elles seront indissociable pendant toute la période de développement. | ||

| + | *[http://www.trenz-electronic.de/de/produkte/fpga-boards/trenz-electronic/te0600.html SPARTAN 6 lx45 chez TRENZ Electronic TE0603 et TE0600 (fourni le 10 octobre 2015)]<br> | ||

| + | *[http://www.trenz-electronic.de/fileadmin/docs/Trenz_Electronic/TE0600-GigaBee_series/TE0600/documents/UM-TE0600-02.pdf Datasheet]<br> | ||

| + | =====Caracteristiques SPARTAN 6 XILINX LX45===== | ||

| + | [[Fichier:Spartan6_logo.jpg|200px|thumb|right|SPARTAN 6 LX45]] | ||

| + | '''General''' | ||

| + | *consommation: 0.6A | ||

| + | *45nm low power process technology with 6-input LUTs | ||

| + | *1080MHz clock management tiles (2 DCM + 1 PLL) | ||

| + | *320MHz Block RAM from 216 - 4824 Kbits | ||

| + | *Memory interface controllers blocks from 0 - 4 | ||

| + | *1.08Gbps SelectIO™ technology | ||

| + | *390MHz DSP48A1 slices from 8 - 180 | ||

| + | *Embedded processing <br> | ||

| + | <br> | ||

| + | Pour plus de détails:<br> | ||

| + | [[Fichier:Caracteristiques_SPARTAN_6_XILINX_LX45.pdf]] | ||

| + | <br> | ||

| + | [http://www.xilinx.com/support/documentation/data_sheets/ds160.pdf General Description]<br> | ||

| + | [http://www.xilinx.com/publications/prod_mktg/Spartan6_Product_Brief.pdf Commerciale presentation]<br> | ||

| + | [http://www.xilinx.com/support/documentation/data_sheets/ds162.pdf Spartan-6 FPGA Electrical Characteristics]<br> | ||

| + | |||

| + | =====Caractéristiques de TE0600 ===== | ||

| + | [[Fichier:TE0600_photo.jpg|300px|thumb|right|TE0600]] | ||

| + | [[Fichier:TE0603_photo.jpg|300px|thumb|right|TE0603]] | ||

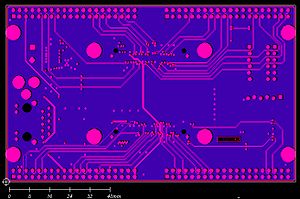

| + | [[Fichier:TE0603_Gerber.jpg|300px|thumb|right|Gerber TE0603]] | ||

| + | Industrial-grade Xilinx Spartan-6 LX FPGA micromodule (LX45 / LX100 / LX150) | ||

| + | * 10/100/1000 tri-speed Gigabit Ethernet transceiver (PHY) | ||

| + | * 2 x 16-bit-wide 1 Gb (128 MB) or 4Gb (512 MB) DDR3 SDRAM | ||

| + | * 128Mb (16 MB) SPI Flash memory (for configuration and operation) accessible through: | ||

| + | * 1Kb Protected 1-Wire EEPROM with SHA-1 Engine | ||

| + | * JTAG port (SPI indirect) | ||

| + | * FPGA configuration through: | ||

| + | * B2B connector | ||

| + | * JTAG port | ||

| + | * SPI Flash memory | ||

| + | * Plug-on module with 2 × 100-pin high-speed hermaphroditic strips | ||

| + | * Up to 52 differential, up to 109 single-ended (+ 1 dual-purpose) FPGA I/O pins available on B2B strips | ||

| + | * 4.0 A x 1.2 V power rail | ||

| + | * 1.5 A x 1.5 V power rail | ||

| + | * 125 MHz reference clock signal | ||

| + | * Single-ended custom oscillator (option) | ||

| + | * eFUSE bit-stream encryption (LX100 or larger) | ||

| + | * 1 user LED | ||

| + | * Evenly-spread supply pins for good signal integrity | ||

| + | * Other assembly options for cost or performance optimization available upon request.<br> | ||

| + | [http://www.trenz-electronic.de/fileadmin/docs/Trenz_Electronic/TE0600-GigaBee_series/TE0600/documents/UM-TE0600-02.pdf Datasheet TE0600]<br> | ||

| + | |||

| + | =====Caractéristiques du TE0603===== | ||

| + | *Board power supply via screw terminals, DC jack | ||

| + | *JTAG header compatible with Xilinx parallel cable III, IV and USB cable HW-USB | ||

| + | *Small form factor: 115x70 mm | ||

| + | *Micro SD connector | ||

| + | *5 Header connectors with up to 114 user IOs | ||

| + | *2 Push-buttons for reset and user function | ||

| + | [http://www.trenz-electronic.de/fileadmin/docs/Trenz_Electronic/TE0600-GigaBee_series/TE0603/documents/UM-TE0603.pdf Datasheet TE0603] <br> | ||

| + | |||

| + | ===== Étude de la carte TE0603===== | ||

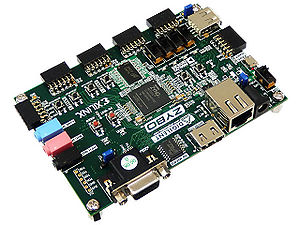

| + | [[Fichier:Zybo.jpg|300px|thumb|right|ZYBO]] | ||

| + | Je vais travailler avec la carte TE0603 en lui ajoutant une socket support pour ajouter une barrette de RAM. En effet, on peut configurer le FPGA pour que ces LUT se transforment en mémoire volatile. Cependant, la taille de ces mémoire reste limité au maximum à 512Mb configurable en 16 ou 32 bits. Mais le CAN branché en amont du FPGA fonctionne à une fréquence de 50MHz, on se rend vite compte que la mémoire RAM va se saturer même si la vitesse de la transmission en aval par le port Ethernet est élevé. <br> | ||

| + | On trouve sur le site [http://www.trenz-electronic.de trenz-electronic.de] des fichiers schematic et typon lisible sous Altium de la carte de TE0603. C'est de ce [http://www.trenz-electronic.de/download/d0/Trenz_Electronic/d1/TE0600-GigaBee_series/d2/TE0603/d3/HW_design.html schéma] que je vais démarrer pour réaliser la carte fille RAM. <br> | ||

| + | |||

| + | En étudiant de plus près le protocole de lecture et d'écriture, il semble possible de créer une carte fille avec juste le support de la barrette physique de RAM. C'est le FPGA qui va se charger de réaliser le "driver" pour accéder en écriture et en lecture les espaces mémoires. | ||

| + | <br><br><br><br> | ||

| + | |||

| + | ====ZYBO==== | ||

| + | C'est une plate-forme de développement d'usage général. Celle-ci intègre un port HDMI, plusieurs ports USB dont un pour la programmation, plusieurs switch, plusieurs boutons poussoirs, un slot pour carte SD et surtout 512Mb de DDR3. Cette carte possède comme autre avantage qu'elle peut booter sur un linux via la carte SD. Ainsi, on peut se connecter en SSH/SCP sur la machine et interagir, émettre et recevoir des données en grande quantité. Je pense que le ZYNQ 7000 est un FPGA très avantageux pour faire du système embarqué. | ||

| + | |||

| + | |||

| + | *[http://digilentinc.com/Products/Detail.cfm?NavPath=2,400,1198&Prod=ZYBO Diligent ZYBO Zynq-7000] (fourni le 26 novembre 2015) | ||

| + | |||

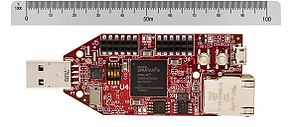

| + | ====LX9 MicroBoard==== | ||

| + | [[Fichier:LX9.jpg|300px|thumb|right|AVNET LX9 MicroBoard]] | ||

| + | *Plateforme Xilinx Spartan-6 FPGA LX9 MicroBoard (ressource personnel) | ||

| + | C'est une plate-forme de développement à faible coût qui permet de travailler avec un SPARTAN 6 et MicroBlaze. Elle possède plusieurs entrées sorties (moins que la TE0600), des leds, un interrupteur et 4 switch très fragiles et un port Ethernet. Cette board vient de mes ressources personnelles mais le modèle étant simple et assez répandu, on trouve beaucoup de tutoriel explicatif sur internet. | ||

| + | <br> | ||

| + | <br> | ||

| + | <br> | ||

| + | <br> | ||

| + | <br> | ||

| + | |||

| + | ===Etude de la problématique=== | ||

| + | ====Étude pour l'ajout de RAM==== | ||

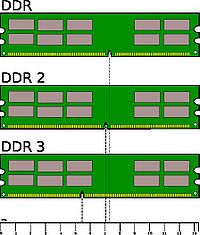

| + | Je m'interroge sur les différentes technologies de RAM, en cherchant sur le net, on trouve des comparatifs et de brefs historiques. En voici des extraits:<br> | ||

| + | '''Historique:''' <br> | ||

| + | [[Fichier:DDR.jpg|200px|thumb|right|Différents types de barrette de RAM]] | ||

| + | <span style="color: grey;">Double Data Rate (DDR) SDRAM starts making name in computer market around 2002 and is evolved from SDR (Single Data Rate) SDRAM. The slight difference between DDR and SDR is that DDR reads data on both the rising and falling edges of the clock signal, enabling a DDR memory module to transfer data twice faster as an SDR memory module. | ||

| + | |||

| + | <span style="color: grey;">After 2 years DDR made name in the market, DDR2 appears in mid-2004. DDR2 achieves a better speed than DDR in providing bandwidth up to 8.5 GB per second. The best thing about DDR2 is that theDDR2 based systems can use memory installed in pairs to run in "dual channel mode" to increase memory throughput even further. | ||

| + | |||

| + | <span style="color: grey;">Nowadays, DDR3 takes place of DDR2 in the computer market. DDR3 is believed to consume less power because it operates at lower voltages and can transfer data at rates up to 12.8 GB per second which is 4.3 GB per second faster than DDR2. DDR3 based systems can address memory modules in banks of 1, 2 or 3. | ||

| + | |||

| + | {| class="wikitable alternance centre" | ||

| + | |+ Comparatif des performances de DDR* RAM | ||

| + | |- | ||

| + | | | ||

| + | ! scope="col" | DDR1 RAM | ||

| + | ! scope="col" | DDR2 RAM | ||

| + | ! scope="col" | DDR3 RAM | ||

| + | |- | ||

| + | ! scope="row" | Nombre de pins | ||

| + | | 184 | ||

| + | | 240 | ||

| + | | 240 | ||

| + | |- | ||

| + | ! scope="row" | Vitesse d'horloge | ||

| + | | 100 MHz à 200 MHz | ||

| + | | 100 MHz à 266 MHz | ||

| + | | 100 MHz à 300 MHz | ||

| + | |- | ||

| + | ! scope="row" | Taux maximum de tranfers | ||

| + | | 200 MT/s à 400 MT/s | ||

| + | | 400 MT/s à 1066 MT/s | ||

| + | | 800 MT/s à 2400 MT/s | ||

| + | |- | ||

| + | ! scope="row" | Tension d'alimentation | ||

| + | | 2.5 V | ||

| + | | 1.8 V | ||

| + | | 1.5 V | ||

| + | |} | ||

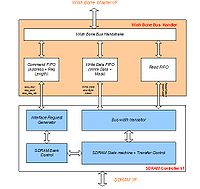

| − | === | + | ====IP pour SDRRAM==== |

| − | == | + | [[Fichier:Sram.jpg|200px|thumb|right|Schéma fonctionnel du driver pour DDR RAM]] |

| − | === | + | *Étude de l'IP pour l'adressage RAM |

| − | === | + | On trouve plusieurs Ip pour adresser des mots mémoires à la carte RAM: |

| − | == | + | **[http://opencores.org/project,sdr_ctrl opencore] |

| − | === | + | **Schéma fonctionnel: |

| − | === | + | <br><br><br><br><br> |

| − | + | ||

| − | === | + | Il semble que le Spartan 6 possède des Memory Controller Blocks (MCBs) qui sont spécialement conçu pour adresser des DRAM (DDR, DDR2 et DDR3). Les MCBs ont une vitesse d'accès supérieur à 800 Mbit/s selon la datasheet du Spartan 6. On peut utiliser l'outil Memory Interface Generator (MIG) qui est disponible dans l'outil CORE Generator de ISE. |

| − | === | + | |

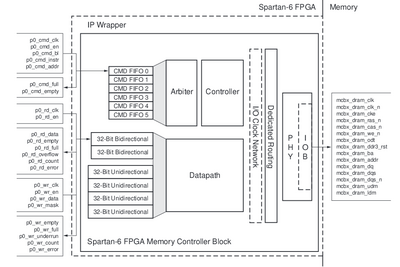

| − | === | + | ====Etude des Memory Controller Blocks==== |

| − | === | + | [[Fichier:MCB.png|400px|thumb|right|Représentation du fonctionnement d'un Memory Controller Block (MCB)]] |

| − | === | + | Il y a trois fonctions principales du point de vue de l'utilisateur: |

| − | === | + | *Lire le port (unidirectionnel) |

| − | === | + | *Écrire sur le port (unidirectionnel) |

| − | === | + | *Lire et écrire sur le port (bi directionnel) |

| − | === | + | On peut voir la représentation du fonctionnement d'un Memory Controller Block (MCB)plusieurs blocks que l'on définit ainsi: |

| − | = | + | *Arbiter ou arbitre: |

| − | + | Il détermine quel port à la priorité pour accéder à la mémoire physique. | |

| − | + | *Controller ou contrôleur: | |

| − | + | Block de contrôle primaire qui convertit de simples requêtes utilisateur en de plus complexes instructions et séquences pour commmuniquer avec la mémoire. | |

| − | + | *Datapath | |

| − | + | Ce block porte le flux de données écrite et lue entre la mémoire physique et l'utilisateur. | |

| + | *Physical Interface (PHY) ou interface physique: | ||

| + | Convertit les instructions du contrôleur en des relations temporelles et signaux adapté à la mémoire DDR pour communiquer avec elle. | ||

| + | *Calibration Logic: | ||

| + | Clalibre l'interface physique (PHY) pour avoir le meilleur rendement. | ||

| + | |||

| + | ===Proposition de solutions=== | ||

| + | ====Récuperation et affichage des données avec la pateforme ZYBO==== | ||

| + | Voici une liste de matériel pour réaliser cette solution: | ||

| + | *Plateforme ZYBO | ||

| + | *Alimentation 5V 3A | ||

| + | *Carte microSD 4Gb (2Gb minimum) | ||

| + | *Cable RJ45 | ||

| + | *Linux type Debian <br> | ||

| + | Voici les différentes étapes à réaliser pour récupérer et afficher les données venant des GPIOs:<br> | ||

| + | |||

| + | =====Téléchargement et installation===== | ||

| + | a°)Telecharger et installer Vivado WebPack de la version la plus récente. [http://www.xilinx.com/support/download.html (Xilinx)] <br> | ||

| + | b°)Télecharger depuis [https://reference.digilentinc.com/zybo:zybo Zybo Resource Center] le fichier zybo_base_system.zip. <br> | ||

| + | c°)Télecharger depuis ce [https://github.com/Digilent/vivado-boards/archive/master.zip lien] les ZYBO board files et placer le dossier source /new/zybo/ dans C:\Xilinx\Vivado\2015.4\data\boards\board_files <br> | ||

| + | d°)Télecharger les fichiers [http://xillybus.com/downloads/xillinux-eval-zybo-1.3c.zip xillinux-eval-zybo-1.3c.zip] et n'en extraire que le dossier bootfiles dans le dossier de travail<br> | ||

| + | e°)Télecharger le fichier [http://xillybus.com/downloads/xillinux-1.3.img.gz xillinux-1.3.img.gz] et extraire son contenu dans le dossier de travail<br> | ||

| + | =====Création d'une carte bootable sur ZYBO===== | ||

| + | [[Fichier:Tuto1.PNG|100px|thumb|right|g°)]] | ||

| + | [[Fichier:Tuto2.PNG|100px|thumb|right|h°)]] | ||

| + | [[Fichier:Tuto3.PNG|100px|thumb|right|j°)]] | ||

| + | [[Fichier:Tuto4.PNG|100px|thumb|right|l°)]] | ||

| + | [[Fichier:Tuto5.PNG|100px|thumb|right|l°)]] | ||

| + | [[Fichier:Tuto6.PNG|100px|thumb|right|l°)]] | ||

| + | [[Fichier:Tuto8.PNG|100px|thumb|right|o°)]] | ||

| + | Dans la suite du tutoriel, je vais présenter comment obtenir le fichier .bit qui permet d'obtenir un accès aux différents ports du FPGA comme les switches, les leds, le HDMI etc. Si vous voulez prendre un fichier tout fait, je vous propose le mien qui est déjà compilé et fonctionnel. On le trouvera dans ce [[fichier: Pack_bit.zip | fichier .zip]] avec un imprim'écran qui montre les registres lié aux différentes interfaces. Ce fichier image est très important pour la partie "récupération" des données. Si vous utilisez ce fichier .zip, sautez directement au point .<br> | ||

| + | f°)Ouvrir avec le logiciel Vivado zybo_base_system\source\vivado\hw\zybo_bsd\zybo_bsd.xpr <br> | ||

| + | g°)Sur la gauche de l'écran, sous IP integrator, choisir Open Block Design <br> | ||

| + | h°)Supprimer l'IP pour adresser les LEDS <br> | ||

| + | i°)On va créer un nouvel IP, tool->Create and Package IP...; next; name-> myLed; next <br> | ||

| + | j°)La fenêtre suivante permet d'ajouter des interfaces. On va créer une interface AX14 pour le peripherique myLed. | ||

| + | *Interface type ->Lite | ||

| + | *Mode ->Slave | ||

| + | *data width ->32 bits | ||

| + | *number of registers ->4 | ||

| + | *Name->S00_AXI <br> | ||

| + | k°)La fenêtre suivante permet de choisir l'option "edit IP"<br> | ||

| + | l°)Dans le projetct manager, ouvrir "myLed_V1..." et ajouter à la ligne 18 : | ||

| + | {| width=10% | ||

| + | |<pre>output wire [3:0] led, </pre> | ||

| + | |} | ||

| + | et à la ligne 400 : | ||

| + | {| width=10% | ||

| + | |<pre> assign led=slv_reg0[3:0];</pre> | ||

| + | |} | ||

| + | |||

| + | |||

| + | m°)Il faut maintenant ajouter l'IP au design. Cliquer sur Open Block Design, puis click droit → Add IP et choisir myLed0. Relier comme sur l'image le I/O de l'IP en cliquant sur « run connection automation ».<br> | ||

| + | n°)Clique droit sur l'IP → create port, le nommer LED sur 4 bit et supprimer le précédent port. Relier le port de sortie à LED.<br> | ||

| + | o°)Dans les sources du Project manager, allez dans constraints, et ouvrir base.xdc et modifier comme sur l'image. <br> | ||

| + | p°) Dans le flow navigator, cliquer sur create bitstream.<br> | ||

| + | |||

| + | =====Préparation et utilisation de la carte µSD===== | ||

| + | q°)Dans notre dossier de travail, nous avons 4 fichiers : | ||

| + | *boot.bin | ||

| + | *devicetree.dtb | ||

| + | *uImage | ||

| + | *le fichier *.bit que l'on vient de générer et que l'on renomme xillydemo.bit | ||

| + | <br> | ||

| + | r°)Monter la carte µSD dans le PC sous linux. Créer une partition de 36Mo en FAT16 et une partition qui prend tout le reste de la place en ext4. Personnellement après de nombreuse tentatives, je recommande GParted.<br> | ||

| + | s°)Copier les quatre fichiers sur la partition de 36Mo.<br> | ||

| + | t°)Éteindre la board avec le switch. Mettre le jumper de boot sur SD. Installer la carte SD dans le slot. Allumer la board.<br> | ||

| + | |||

| + | Vous pouvez maintenant brancher un câble HDMI ou VGA à la board pour y connecter un écran, ainsi qu'un clavier pour faire la configuration et l'installation de Ubuntu. Le nom d'utilisateur est root et le mot de passe est toor. Le mieux est de faire un apt-get update, puis un apt-get upgrade pour mettre à jour les paquets. Il est maintenant nécessaire d'installer les paquets pour ssh si ce n'est pas déjà fait. Il est aussi nécessaire d'installer python.<br> | ||

| + | =====Récupération des données des GPIOs===== | ||

| + | C'est là que le fichier d'adressage qui se situe dans Pack_bit si vous n'avez pas fait votre propre bitstream ou dans Vivado → Open Block Design → Adress Editor, va nous servir. | ||

| + | On peut utiliser nmap pour scanner son réseau et trouver l'adresse ip de la board ZYBO. | ||

| + | Une fois connecté, on va récupérer les données des switchs et écrire leur valeur dans un fichier. Voici un code en python qui récupère les données depuis des adresses mémoire dans /dev/mem. Le code est assez simple et efficace. L'astuce consiste à mettre en relation les offset que l'on voit avec les adresses que l'on a attribué avec l'Adress Editor dans Vivado :<br> | ||

| + | |||

| + | On voit que les offset des LED et des SWITCH correspondent. | ||

| + | J'ai ensuite crée un serveur apache sur le linux du ZYBO et j'ai affiché les données que j'ai collécté sur un graphique que je peux atteindre en tapant l'adresse ip de la machine.<br> | ||

| + | |||

| + | J'ai pu mesurer la vitesse d'acquisition des données, celle ci n'est pas très élevé. On obtient 180 Ko/s. Ce pendant cette méthode est utile si on veut récupérer les données qui sont dans la RAM. En effet, j'ai pu tester des codes en C qui permettent de récupérer directement les données qui sont dans la RAM à partir du linux embarqué. <br><br><br> | ||

| + | [[Fichier:Tuto9.PNG|500px|thumb|center]]<br><br> | ||

| + | C'est là que le fichier d'adressage qui se situe dans Pack_bit si vous n'avez pas fait votre propre bitstream ou dans Vivado → Open Block Design → Adress Editor, va nous servir. On peut utiliser nmap pour scanner son réseau et trouver l'adresse ip de la board ZYBO. Une fois connecté, on va récupérer les données des switchs et écrire leur valeur dans un fichier. Voici un code en python qui récupère les données depuis des adresses mémoire dans /dev/mem. Le code est assez simple et efficace. L'astuce consiste à mettre en relation les offset que l'on voit avec les adresses que l'on a attribué avec l'Adress Editor dans Vivado:<br><br> | ||

| + | [[Fichier:Adress_map.PNG|500px|thumb|center]] | ||

| + | <br><br><br> | ||

| + | On voit que les offset des LED et des SWITCH correspondent. J'ai ensuite crée un serveur apache sur le linux du ZYBO et j'ai affiché les données que j'ai collécté sur un graphique que je peux atteindre en tapant l'adresse ip de la machine. J'ai pu mesurer la vitesse d'acquisition des données, celle ci n'est pas très élevé. On obtient 180 Ko/s. Ce pendant cette méthode est utile si on veut récupérer les données qui sont dans la RAM. En effet, j'ai pu tester des codes en C qui permettent de récupérer directement les données qui sont dans la RAM à partir du linux embarqué. | ||

| + | |||

| + | ====Direct Memory Acess==== | ||

| + | Tout d'abord, Xilinx marque une différence entre AXI DMA et AXI VDMA (Video Direct Memory Acess). AXI DMA fait réference à l'accès traditionnel à la mémoire DDR en transférant arbitrairement un flux de données depuis le FPGA vers la mémoire DDR. VDMA ajoute un mécanisme de stockage synchrone par frame en utilisant un ring buffer dans la DDR. | ||

| + | <br> | ||

| + | AXI DMA distingue deux voies : MM2S (Memory-Mapped to Stream) qui transporte les données de la DDR au FPGA et S2MM (Stream to Memory-Mapped) qui transporte arbitrairement le flux de données à la DDR. | ||

| + | <br> | ||

| + | [[Fichier:DMA.PNG|500px|thumb|center]] | ||

| + | <br> | ||

| + | Utiliser la board Zybo permet de récupérer les données de manière avantageuse. Un simple script python permet d'accéder aux données et de les inscrire dans un fichier. L'avantage de l'architecture AXI DMA sur un ZYNQ 7000 est que l’architecture hybride facilite les choses. Permettant au FPGA de fonctionner avec les avantages de fonctionner en partie avec des lignes de commande. Ici la mémoire DDR va être partagée entre le processeur Cortex et le FPGA. | ||

| + | <br> | ||

| + | Dans le fichier RAR rendu en Annexe, vous trouverez un projet nommé AXI_DMA qui est le projet d'accès à la mémoire par DMA. Celui-ci fonctionne avec le SDK, il utilise un bloc FIFO pour le test. Il faut remplacer ce bloc par un bloc d'acquisition des GPIO. Pour accéder au debug, il faut exporter le bitstream qui est généré, générer un code en C/C++ et le lancer dans le processeur cortex. Pour l'instant, je n'arrive pas à debugger le programme que j'ai fait car je ne comprends pas tous les éléments que me renvoie la liaison série. | ||

| + | <br> | ||

| + | [[Fichier:DesignAXI DAM.PNG|500px|thumb|center]] | ||

| + | <br> | ||

| + | À droite on voit l'IP « processing_system7_0 » qui permet l'interaction entre les deux cœurs et le partage de certaines ressources comme les GPIOs et la DDR. Au centre on voit l'IP AXI_DMA qui est relié au bloc FIFO qu'il faut remplacer par un bloc GPIO que l'on peut trouver dans le projet « zybo_base_system.backup_bitstream_linux ». On voit aussi le bloc processing7_0_axi_periph qui permet un ordonnancement des périphériques entre les deux cœurs. Enfin, on trouve un bloc « xlconcat0 » qui permet d'utiliser le bloc DMA en mode « polling » grâce au déclenchement d'interruption sur le Zynq Processing System (PS). | ||

| + | <br> | ||

| + | Le mode « polling » consiste à faire attendre au PS que le FPGA lui dise de lire les données. C'est une méthode par interruption. Ainsi, il faut modifier l'IP de manière à ce que lorsque la mémoire DDR est pleine l'interruption se déclenche pour que le PS vienne inscrire les données dans un fichier. | ||

| + | <br> | ||

| + | Cette méthode peut fonctionner mais il faut bien maîtriser le flow de conception pour y arriver. Je conseille de commencer par la récupération et le stockage de données dans la DDR de la ZYBO. | ||

| + | |||

| + | |||

| + | ==Analyse et conclusion== | ||

| + | Pendant toute la durée du PFE, j'ai pu m’intéresser au sujet de la mémoire SDRAM et aux FPGA. J'ai eu l'occasion de comparer différentes techniques de développement et de tester de nombreux programmes. J'ai pu faire des recherches approfondis sur le concept de mémoire pour pouvoir mettre en place une structure de réflexion autours de mon sujet. J'ai eu l'occasion de parler avec un ingénieur hardware en personne du sujet et de communiquer sur des forums pour trouver des solutions. J'ai eu la chance d'effectuer des recherches sur des sujets autant pratiques que théoriques ce qui m'a permis de mettre en relation les deux types de savoir. J'ai pu me familiarisé avec une board FPGA tel que la ZYBO, ce qui m'a donné l'envie de continuer, et d'investir dans ce type de plate-forme. J'aimerai à l'avenir que ce sujet soit poursuivit pour aboutir à sa réussite totale, pas seulement pour les besoins du laboratoire, mais aussi pour que les possibilités d'une telle fonctionnalités servent à d'autres projets.<br> | ||

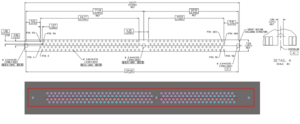

| + | ==Fichiers== | ||

| + | [[Fichier:DDR connecteur datasheet.png|300px|thumb|right|]] | ||

| + | *Empreinte sous Altium Designer pour le connecteur DDR3 | ||

| + | <br><br><br><br><br> | ||

| + | <br> | ||

| + | <br> | ||

| + | |||

| + | ==Shopping== | ||

| + | *[http://www.mouser.fr/ProductDetail/FCI/10081530-12207LF/?qs=sGAEpiMZZMu51HMau1GEUGmiHfa8/gTAo1M2%252bNESSU0%3d Connecteur DDR3] 1.5€ ([http://portal.fciconnect.com/Comergent/en/US/adirect/fci;jsessionid=FEFFAFAD5839598353F129F4194CC82E?cmd=catProductDetail&entryPoint=adirect&messageType=catProductDetail&showAddButton=true&productID=1008153012207LF datasheet]) | ||

| + | *[http://www.mouser.fr/ProductDetail/FCI/10005639-11109LF/?qs=sGAEpiMZZMu51HMau1GEUBTEbqSTMcBDcRDLdGvDZHE%3d Connecteur DDR2] 2€ ([http://www.mouser.com/ds/2/154/gs-12-251-532922.pdf datasheet]) | ||

| + | *[http://www.mouser.fr/ProductDetail/TE-Connectivity-AMP/5390241-4/?qs=sGAEpiMZZMu51HMau1GEUC3LrSDvJPJ82YYPKc6FyEY%3d Connecteur DDR1] 4.5€ ([http://www.mouser.com/ds/2/418/NG_CD_5390241_E-668131.pdf datasheet]) | ||

| + | *Recuperation de DDR1 au service informatique de Polytech | ||

| + | |||

| + | ==Sources== | ||

| + | [http://www.trenz-electronic.de/download/d0/Trenz_Electronic/d1/TE0600-GigaBee_series/d2/TE0603.html Fiche commerciale TE0600] <br> | ||

| + | [http://www.fpga4fun.com/FPGAinfo1.html FPGA généralité]<br> | ||

| + | [http://www.xilinx.com/support/documentation/user_guides/ug388.pdf Guide Xilinx pour le design avec les MCB (Chapitre 3) ] <br> | ||

| + | [http://www.xilinx.com/support/documentation/ip_documentation/mig/v3_92/ug416.pdf Guide Xilinx pour le design avec l'outil MIG (page 9)]<br> | ||

| + | [http://claude.lahache.free.fr/mapage2/lignes.pdf Cours sur les lignes de propagations]<br> | ||

| + | [http://hallofitmage.blogspot.fr/2012/03/difference-between-ddr-ddr2-and-ddr3.html Frautte Nihilus] <br>[https://en.wikipedia.org/wiki/DIMM Wikipédia DIMM]<br> | ||

Version actuelle datée du 16 mars 2016 à 15:24

Sommaire

Cahier des charges

Présentation générale du projet

Dénomination du sujet par les enseignants

| Objectif | Réaliser une plate-forme de mesure de la consommation d'équipement électroniques |

|---|---|

| Description | La consommation des équipements électroniques est devenue un enjeu majeur puisque les équipements sont très souvent utilisés en situation de mobilité. La réduction de la consommation passe par la compréhension des sources de consommation que ce soit par le logiciel ou par le matériel.

Afin de comprendre les mécanismes de consommation, il est nécessaire de pouvoir mesurer le courant des différents composants d'un système. Dans ce projet, nous proposons la réalisation d'une plate-forme permettant la mesure de courant. Cette plate-forme devra être ouverte et facilement reconfigurable (ajout / retrait de voies de mesures, filtrage des mesures, ...) La plate-forme sera constituée de :

|

Contexte

Dans le cadre d'une réalisation de projet de fin d'étude, on se propose de réaliser un "data logger". Durant les semaines à venir, je vais travailler sur un dispositif qui stockera des données numériques envoyé depuis un convertisseur analogique numérique dans une barrette de RAM avant de les rendre accessible par une liaison RS232. Le but de se projet est de compléter le panel de technologie disponible pour un laboratoire qui possède une...

Objectif du projet

- stocker en RAM une série de donnée le plus rapidement possible

- construire interface permettant de recuperer les infomations via un RJ45 protocole Ethernet

- rendre modulaire le code en permettant de modifier facilement de la taille des mots d'entrée (passer de 8 bits à 10 puis 16 ...)

- rendre modulaire le code en permettant d'ajouter un fréquencemètre

- développer une carte support pour le LX45 maitriser les temps de propagations des signaux sur le typon, en direction de la barrette de RAM

Étapes du projet

Le projet va se dérouler en plusieurs étapes.

1)Etude des plates-formes de programmation

2)Etude de la problématique

3)Proposition de solutions et argumentaire

Choix techniques : matériel, logiciels, sources

Suivi des étapes du Projet

Etude des plates-formes de programmation

TE0600 & TE0603

La board que m'ont fournie les encadrants se compose se compose d'une carte mère et d'une carte support. La carte mère, nommé TE0600 est composé d'un FPGA Xilinx SPARTAN 6 LX45. C'est le "cerveau" du projet qui vient se brancher sur une carte support qui me servira au développement (programmation, IOs, carte mémoire, alimentation, Ethernet...). Celle ci se nomme TE0603. Elles seront indissociable pendant toute la période de développement.

Caracteristiques SPARTAN 6 XILINX LX45

General

- consommation: 0.6A

- 45nm low power process technology with 6-input LUTs

- 1080MHz clock management tiles (2 DCM + 1 PLL)

- 320MHz Block RAM from 216 - 4824 Kbits

- Memory interface controllers blocks from 0 - 4

- 1.08Gbps SelectIO™ technology

- 390MHz DSP48A1 slices from 8 - 180

- Embedded processing

Pour plus de détails:

Fichier:Caracteristiques SPARTAN 6 XILINX LX45.pdf

General Description

Commerciale presentation

Spartan-6 FPGA Electrical Characteristics

Caractéristiques de TE0600

Industrial-grade Xilinx Spartan-6 LX FPGA micromodule (LX45 / LX100 / LX150)

- 10/100/1000 tri-speed Gigabit Ethernet transceiver (PHY)

- 2 x 16-bit-wide 1 Gb (128 MB) or 4Gb (512 MB) DDR3 SDRAM

- 128Mb (16 MB) SPI Flash memory (for configuration and operation) accessible through:

- 1Kb Protected 1-Wire EEPROM with SHA-1 Engine

- JTAG port (SPI indirect)

- FPGA configuration through:

- B2B connector

- JTAG port

- SPI Flash memory

- Plug-on module with 2 × 100-pin high-speed hermaphroditic strips

- Up to 52 differential, up to 109 single-ended (+ 1 dual-purpose) FPGA I/O pins available on B2B strips

- 4.0 A x 1.2 V power rail

- 1.5 A x 1.5 V power rail

- 125 MHz reference clock signal

- Single-ended custom oscillator (option)

- eFUSE bit-stream encryption (LX100 or larger)

- 1 user LED

- Evenly-spread supply pins for good signal integrity

- Other assembly options for cost or performance optimization available upon request.

Caractéristiques du TE0603

- Board power supply via screw terminals, DC jack

- JTAG header compatible with Xilinx parallel cable III, IV and USB cable HW-USB

- Small form factor: 115x70 mm

- Micro SD connector

- 5 Header connectors with up to 114 user IOs

- 2 Push-buttons for reset and user function

Étude de la carte TE0603

Je vais travailler avec la carte TE0603 en lui ajoutant une socket support pour ajouter une barrette de RAM. En effet, on peut configurer le FPGA pour que ces LUT se transforment en mémoire volatile. Cependant, la taille de ces mémoire reste limité au maximum à 512Mb configurable en 16 ou 32 bits. Mais le CAN branché en amont du FPGA fonctionne à une fréquence de 50MHz, on se rend vite compte que la mémoire RAM va se saturer même si la vitesse de la transmission en aval par le port Ethernet est élevé.

On trouve sur le site trenz-electronic.de des fichiers schematic et typon lisible sous Altium de la carte de TE0603. C'est de ce schéma que je vais démarrer pour réaliser la carte fille RAM.

En étudiant de plus près le protocole de lecture et d'écriture, il semble possible de créer une carte fille avec juste le support de la barrette physique de RAM. C'est le FPGA qui va se charger de réaliser le "driver" pour accéder en écriture et en lecture les espaces mémoires.

ZYBO

C'est une plate-forme de développement d'usage général. Celle-ci intègre un port HDMI, plusieurs ports USB dont un pour la programmation, plusieurs switch, plusieurs boutons poussoirs, un slot pour carte SD et surtout 512Mb de DDR3. Cette carte possède comme autre avantage qu'elle peut booter sur un linux via la carte SD. Ainsi, on peut se connecter en SSH/SCP sur la machine et interagir, émettre et recevoir des données en grande quantité. Je pense que le ZYNQ 7000 est un FPGA très avantageux pour faire du système embarqué.

- Diligent ZYBO Zynq-7000 (fourni le 26 novembre 2015)

LX9 MicroBoard

- Plateforme Xilinx Spartan-6 FPGA LX9 MicroBoard (ressource personnel)

C'est une plate-forme de développement à faible coût qui permet de travailler avec un SPARTAN 6 et MicroBlaze. Elle possède plusieurs entrées sorties (moins que la TE0600), des leds, un interrupteur et 4 switch très fragiles et un port Ethernet. Cette board vient de mes ressources personnelles mais le modèle étant simple et assez répandu, on trouve beaucoup de tutoriel explicatif sur internet.

Etude de la problématique

Étude pour l'ajout de RAM

Je m'interroge sur les différentes technologies de RAM, en cherchant sur le net, on trouve des comparatifs et de brefs historiques. En voici des extraits:

Historique:

Double Data Rate (DDR) SDRAM starts making name in computer market around 2002 and is evolved from SDR (Single Data Rate) SDRAM. The slight difference between DDR and SDR is that DDR reads data on both the rising and falling edges of the clock signal, enabling a DDR memory module to transfer data twice faster as an SDR memory module.

After 2 years DDR made name in the market, DDR2 appears in mid-2004. DDR2 achieves a better speed than DDR in providing bandwidth up to 8.5 GB per second. The best thing about DDR2 is that theDDR2 based systems can use memory installed in pairs to run in "dual channel mode" to increase memory throughput even further.

Nowadays, DDR3 takes place of DDR2 in the computer market. DDR3 is believed to consume less power because it operates at lower voltages and can transfer data at rates up to 12.8 GB per second which is 4.3 GB per second faster than DDR2. DDR3 based systems can address memory modules in banks of 1, 2 or 3.

| DDR1 RAM | DDR2 RAM | DDR3 RAM | |

|---|---|---|---|

| Nombre de pins | 184 | 240 | 240 |

| Vitesse d'horloge | 100 MHz à 200 MHz | 100 MHz à 266 MHz | 100 MHz à 300 MHz |

| Taux maximum de tranfers | 200 MT/s à 400 MT/s | 400 MT/s à 1066 MT/s | 800 MT/s à 2400 MT/s |

| Tension d'alimentation | 2.5 V | 1.8 V | 1.5 V |

IP pour SDRRAM

- Étude de l'IP pour l'adressage RAM

On trouve plusieurs Ip pour adresser des mots mémoires à la carte RAM:

- opencore

- Schéma fonctionnel:

Il semble que le Spartan 6 possède des Memory Controller Blocks (MCBs) qui sont spécialement conçu pour adresser des DRAM (DDR, DDR2 et DDR3). Les MCBs ont une vitesse d'accès supérieur à 800 Mbit/s selon la datasheet du Spartan 6. On peut utiliser l'outil Memory Interface Generator (MIG) qui est disponible dans l'outil CORE Generator de ISE.

Etude des Memory Controller Blocks

Il y a trois fonctions principales du point de vue de l'utilisateur:

- Lire le port (unidirectionnel)

- Écrire sur le port (unidirectionnel)

- Lire et écrire sur le port (bi directionnel)

On peut voir la représentation du fonctionnement d'un Memory Controller Block (MCB)plusieurs blocks que l'on définit ainsi:

- Arbiter ou arbitre:

Il détermine quel port à la priorité pour accéder à la mémoire physique.

- Controller ou contrôleur:

Block de contrôle primaire qui convertit de simples requêtes utilisateur en de plus complexes instructions et séquences pour commmuniquer avec la mémoire.

- Datapath

Ce block porte le flux de données écrite et lue entre la mémoire physique et l'utilisateur.

- Physical Interface (PHY) ou interface physique:

Convertit les instructions du contrôleur en des relations temporelles et signaux adapté à la mémoire DDR pour communiquer avec elle.

- Calibration Logic:

Clalibre l'interface physique (PHY) pour avoir le meilleur rendement.

Proposition de solutions

Récuperation et affichage des données avec la pateforme ZYBO

Voici une liste de matériel pour réaliser cette solution:

- Plateforme ZYBO

- Alimentation 5V 3A

- Carte microSD 4Gb (2Gb minimum)

- Cable RJ45

- Linux type Debian

Voici les différentes étapes à réaliser pour récupérer et afficher les données venant des GPIOs:

Téléchargement et installation

a°)Telecharger et installer Vivado WebPack de la version la plus récente. (Xilinx)

b°)Télecharger depuis Zybo Resource Center le fichier zybo_base_system.zip.

c°)Télecharger depuis ce lien les ZYBO board files et placer le dossier source /new/zybo/ dans C:\Xilinx\Vivado\2015.4\data\boards\board_files

d°)Télecharger les fichiers xillinux-eval-zybo-1.3c.zip et n'en extraire que le dossier bootfiles dans le dossier de travail

e°)Télecharger le fichier xillinux-1.3.img.gz et extraire son contenu dans le dossier de travail

Création d'une carte bootable sur ZYBO

Dans la suite du tutoriel, je vais présenter comment obtenir le fichier .bit qui permet d'obtenir un accès aux différents ports du FPGA comme les switches, les leds, le HDMI etc. Si vous voulez prendre un fichier tout fait, je vous propose le mien qui est déjà compilé et fonctionnel. On le trouvera dans ce Fichier:Pack bit.zip avec un imprim'écran qui montre les registres lié aux différentes interfaces. Ce fichier image est très important pour la partie "récupération" des données. Si vous utilisez ce fichier .zip, sautez directement au point .

f°)Ouvrir avec le logiciel Vivado zybo_base_system\source\vivado\hw\zybo_bsd\zybo_bsd.xpr

g°)Sur la gauche de l'écran, sous IP integrator, choisir Open Block Design

h°)Supprimer l'IP pour adresser les LEDS

i°)On va créer un nouvel IP, tool->Create and Package IP...; next; name-> myLed; next

j°)La fenêtre suivante permet d'ajouter des interfaces. On va créer une interface AX14 pour le peripherique myLed.

- Interface type ->Lite

- Mode ->Slave

- data width ->32 bits

- number of registers ->4

- Name->S00_AXI

k°)La fenêtre suivante permet de choisir l'option "edit IP"

l°)Dans le projetct manager, ouvrir "myLed_V1..." et ajouter à la ligne 18 :

output wire [3:0] led, |

et à la ligne 400 :

assign led=slv_reg0[3:0]; |

m°)Il faut maintenant ajouter l'IP au design. Cliquer sur Open Block Design, puis click droit → Add IP et choisir myLed0. Relier comme sur l'image le I/O de l'IP en cliquant sur « run connection automation ».

n°)Clique droit sur l'IP → create port, le nommer LED sur 4 bit et supprimer le précédent port. Relier le port de sortie à LED.

o°)Dans les sources du Project manager, allez dans constraints, et ouvrir base.xdc et modifier comme sur l'image.

p°) Dans le flow navigator, cliquer sur create bitstream.

Préparation et utilisation de la carte µSD

q°)Dans notre dossier de travail, nous avons 4 fichiers :

- boot.bin

- devicetree.dtb

- uImage

- le fichier *.bit que l'on vient de générer et que l'on renomme xillydemo.bit

r°)Monter la carte µSD dans le PC sous linux. Créer une partition de 36Mo en FAT16 et une partition qui prend tout le reste de la place en ext4. Personnellement après de nombreuse tentatives, je recommande GParted.

s°)Copier les quatre fichiers sur la partition de 36Mo.

t°)Éteindre la board avec le switch. Mettre le jumper de boot sur SD. Installer la carte SD dans le slot. Allumer la board.

Vous pouvez maintenant brancher un câble HDMI ou VGA à la board pour y connecter un écran, ainsi qu'un clavier pour faire la configuration et l'installation de Ubuntu. Le nom d'utilisateur est root et le mot de passe est toor. Le mieux est de faire un apt-get update, puis un apt-get upgrade pour mettre à jour les paquets. Il est maintenant nécessaire d'installer les paquets pour ssh si ce n'est pas déjà fait. Il est aussi nécessaire d'installer python.

Récupération des données des GPIOs

C'est là que le fichier d'adressage qui se situe dans Pack_bit si vous n'avez pas fait votre propre bitstream ou dans Vivado → Open Block Design → Adress Editor, va nous servir.

On peut utiliser nmap pour scanner son réseau et trouver l'adresse ip de la board ZYBO.

Une fois connecté, on va récupérer les données des switchs et écrire leur valeur dans un fichier. Voici un code en python qui récupère les données depuis des adresses mémoire dans /dev/mem. Le code est assez simple et efficace. L'astuce consiste à mettre en relation les offset que l'on voit avec les adresses que l'on a attribué avec l'Adress Editor dans Vivado :

On voit que les offset des LED et des SWITCH correspondent.

J'ai ensuite crée un serveur apache sur le linux du ZYBO et j'ai affiché les données que j'ai collécté sur un graphique que je peux atteindre en tapant l'adresse ip de la machine.

J'ai pu mesurer la vitesse d'acquisition des données, celle ci n'est pas très élevé. On obtient 180 Ko/s. Ce pendant cette méthode est utile si on veut récupérer les données qui sont dans la RAM. En effet, j'ai pu tester des codes en C qui permettent de récupérer directement les données qui sont dans la RAM à partir du linux embarqué.

C'est là que le fichier d'adressage qui se situe dans Pack_bit si vous n'avez pas fait votre propre bitstream ou dans Vivado → Open Block Design → Adress Editor, va nous servir. On peut utiliser nmap pour scanner son réseau et trouver l'adresse ip de la board ZYBO. Une fois connecté, on va récupérer les données des switchs et écrire leur valeur dans un fichier. Voici un code en python qui récupère les données depuis des adresses mémoire dans /dev/mem. Le code est assez simple et efficace. L'astuce consiste à mettre en relation les offset que l'on voit avec les adresses que l'on a attribué avec l'Adress Editor dans Vivado:

On voit que les offset des LED et des SWITCH correspondent. J'ai ensuite crée un serveur apache sur le linux du ZYBO et j'ai affiché les données que j'ai collécté sur un graphique que je peux atteindre en tapant l'adresse ip de la machine. J'ai pu mesurer la vitesse d'acquisition des données, celle ci n'est pas très élevé. On obtient 180 Ko/s. Ce pendant cette méthode est utile si on veut récupérer les données qui sont dans la RAM. En effet, j'ai pu tester des codes en C qui permettent de récupérer directement les données qui sont dans la RAM à partir du linux embarqué.

Direct Memory Acess

Tout d'abord, Xilinx marque une différence entre AXI DMA et AXI VDMA (Video Direct Memory Acess). AXI DMA fait réference à l'accès traditionnel à la mémoire DDR en transférant arbitrairement un flux de données depuis le FPGA vers la mémoire DDR. VDMA ajoute un mécanisme de stockage synchrone par frame en utilisant un ring buffer dans la DDR.

AXI DMA distingue deux voies : MM2S (Memory-Mapped to Stream) qui transporte les données de la DDR au FPGA et S2MM (Stream to Memory-Mapped) qui transporte arbitrairement le flux de données à la DDR.

Utiliser la board Zybo permet de récupérer les données de manière avantageuse. Un simple script python permet d'accéder aux données et de les inscrire dans un fichier. L'avantage de l'architecture AXI DMA sur un ZYNQ 7000 est que l’architecture hybride facilite les choses. Permettant au FPGA de fonctionner avec les avantages de fonctionner en partie avec des lignes de commande. Ici la mémoire DDR va être partagée entre le processeur Cortex et le FPGA.

Dans le fichier RAR rendu en Annexe, vous trouverez un projet nommé AXI_DMA qui est le projet d'accès à la mémoire par DMA. Celui-ci fonctionne avec le SDK, il utilise un bloc FIFO pour le test. Il faut remplacer ce bloc par un bloc d'acquisition des GPIO. Pour accéder au debug, il faut exporter le bitstream qui est généré, générer un code en C/C++ et le lancer dans le processeur cortex. Pour l'instant, je n'arrive pas à debugger le programme que j'ai fait car je ne comprends pas tous les éléments que me renvoie la liaison série.

À droite on voit l'IP « processing_system7_0 » qui permet l'interaction entre les deux cœurs et le partage de certaines ressources comme les GPIOs et la DDR. Au centre on voit l'IP AXI_DMA qui est relié au bloc FIFO qu'il faut remplacer par un bloc GPIO que l'on peut trouver dans le projet « zybo_base_system.backup_bitstream_linux ». On voit aussi le bloc processing7_0_axi_periph qui permet un ordonnancement des périphériques entre les deux cœurs. Enfin, on trouve un bloc « xlconcat0 » qui permet d'utiliser le bloc DMA en mode « polling » grâce au déclenchement d'interruption sur le Zynq Processing System (PS).

Le mode « polling » consiste à faire attendre au PS que le FPGA lui dise de lire les données. C'est une méthode par interruption. Ainsi, il faut modifier l'IP de manière à ce que lorsque la mémoire DDR est pleine l'interruption se déclenche pour que le PS vienne inscrire les données dans un fichier.

Cette méthode peut fonctionner mais il faut bien maîtriser le flow de conception pour y arriver. Je conseille de commencer par la récupération et le stockage de données dans la DDR de la ZYBO.

Analyse et conclusion

Pendant toute la durée du PFE, j'ai pu m’intéresser au sujet de la mémoire SDRAM et aux FPGA. J'ai eu l'occasion de comparer différentes techniques de développement et de tester de nombreux programmes. J'ai pu faire des recherches approfondis sur le concept de mémoire pour pouvoir mettre en place une structure de réflexion autours de mon sujet. J'ai eu l'occasion de parler avec un ingénieur hardware en personne du sujet et de communiquer sur des forums pour trouver des solutions. J'ai eu la chance d'effectuer des recherches sur des sujets autant pratiques que théoriques ce qui m'a permis de mettre en relation les deux types de savoir. J'ai pu me familiarisé avec une board FPGA tel que la ZYBO, ce qui m'a donné l'envie de continuer, et d'investir dans ce type de plate-forme. J'aimerai à l'avenir que ce sujet soit poursuivit pour aboutir à sa réussite totale, pas seulement pour les besoins du laboratoire, mais aussi pour que les possibilités d'une telle fonctionnalités servent à d'autres projets.

Fichiers

- Empreinte sous Altium Designer pour le connecteur DDR3

Shopping

- Connecteur DDR3 1.5€ (datasheet)

- Connecteur DDR2 2€ (datasheet)

- Connecteur DDR1 4.5€ (datasheet)

- Recuperation de DDR1 au service informatique de Polytech

Sources

Fiche commerciale TE0600

FPGA généralité

Guide Xilinx pour le design avec les MCB (Chapitre 3)

Guide Xilinx pour le design avec l'outil MIG (page 9)

Cours sur les lignes de propagations

Frautte Nihilus

Wikipédia DIMM