Communication série, 2013/2014, TD2

Sommaire

Introduction

Partie Electronique

Séance n°1

Nous avons tout d’abord commencé par faire le tutoriel afin de nous familiariser avec le logiciel altium designer. Nous avons ensuite réfléchi à une solution pour l’émission mais nous nous sommes finalement tournés vers la réception qui était plus facile à réaliser.

Nous avons tout d’abord pensé à un registre à décalage qui nous permettrait de convertir de parallèle vers série.

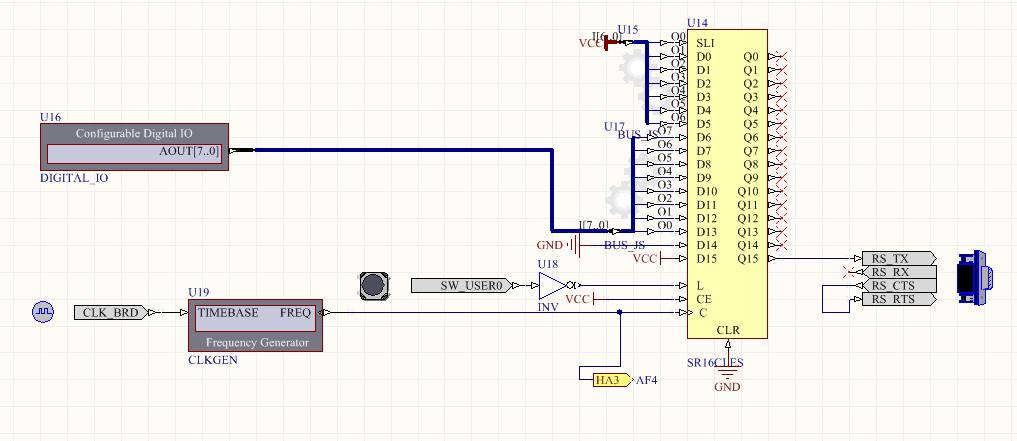

Puis nous avons commencé à réaliser ce montage que nous avons terminé à la 2e séance :

Séance n°2

Lors de la deuxième séance, nous avons donc fini la partie réception. Nous avons inséré un Digital IO (DIO) afin de pouvoir rentrer le bus de données directement à partir du logiciel altium designer. Puis nous avons inséré un bouton poussoir SW_USER0 dans le montage.

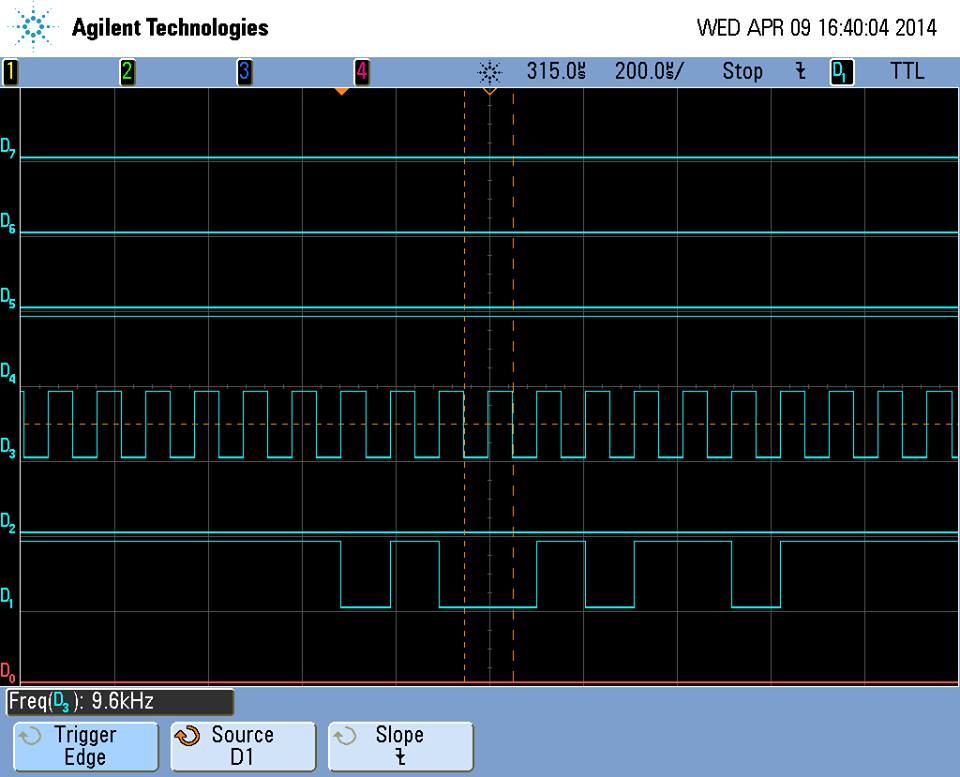

Nous avons ensuite implanté notre partie réception sur la nanoboard. On a donc utilisé le DIO et inséré le mot 0110 1001. Avec un bit de start à 0 et un bit de stop à 1, nous avons pu observer grâce à l'analyseur numérique :

On observe sur D3 le signal de la clock et sur D1 la réception.

Sur D3 :

On oberve la clock à une fréquence de 9600 Hz.

Sur D1 :

- Initialement à 1

- Bit de start à 0 au front montant de la clock

- Le mot de 8 bits : on observe 1001 0110 mais le poids faible est en tête donc le mot est inversé et est donc bien 0110 1001

- Le bit de stop à 1

- Finalement à 1 (le bit de stop n'est donc pas réellement visible car il est confondu avec l'initialisation qui est à 1)

Les résultats se sont donc avérés concluants et nous avons ensuite pu passer à la partie émission qui s’est avérée plus compliquée.

Séance n°3

Pour la partie émission, nous avions besoin de deux horloges :

- La première à une fréquence de 9600 Hz

- La seconde à une fréquence de 2x9600 Hz pour générer une horloge décalée au milieu de chaque bit pour les détecter correctement.

Nous avions ensuite besoin de :

- un multiplexeur qui servait à activer soit la clock à 9600 Hz soit celle à 2x9600 Hz

- un compteur qui servait à compter le nombre de tops d'horloge

- une bascule D qui servait à savoir quand activer la CE du compteur (elle est activée lorsque le compteur est <1 c'est à dire =0)

- un registre à décalage SR16 qui permettait la conversion série vers parallèle

- deux comparateurs :

_ L'un servait à comparer le compteur à 1 afin de savoir quand activer la bascule D (lorsque compteur < 1) ou activer la clock à 9600 Hz (lorsque compteur > 1)

_ L'autre servait à comparer le compteur à 10 afin de savoir quand activer le clear du compteur et de la bascule (lorsque le compteur > 10)

Nous sommes arrivés à une solution qui fonctionnait de temps en temps voir pas du tout lors des tests. Nous avons donc du trouver l’erreur en plaçant des plusieurs endroits stratégiques afin d’observer l’évolution des différents circuits logiques. Nous avons ainsi trouvé d’où venait l’erreur, il s’agissait en fait de la bascule qui ne s’activait pas. Par la suite nous avons remarqué qu’elle était synchrone et attendait donc un top d’horloge pour faire le clear, mais ce top d’horloge qui n’arrivait jamais. Lorsque nous l’avons remplacée par une bascule asynchrone, le clear fonctionnait correctement ainsi que tout le montage.

Nous avons rassemblé puis testé le tout (émission + réception) via la nanoboard et une liaison fournie par notre enseignant en essayant l’émission et la réception de caractères. Le test nous a confirmé que ça fonctionnait et a donc été validé par l’enseignant.