Contrôle de sonar, 2011/2012, TD1

Sommaire

Projet sonar

Participants

Membre de l'équipe: Bonvalet Quentin, Boudjema Samir, Robin Gouenard

Objectif global

A travers ce projet, nous devons réaliser la partie électronique d'un sonar dans le cadre de l'émission et la réception d'un signal mais aussi pouvoir communiquer avec ce sonar par l'intermédiaire d'une interface (PC puis foxboard), afin d'effectuer une action ou recevoir une information par exemple.

Avancement du projet

Objectif de la séance 1

Partie électronique

L'objectif de cette séance est de comprendre le sujet ; puis dans un deuxième temps nous devons nous familiariser avec Altium et la nanoboard.

A partir d'Altium et d'une nanoboard, nous devons donc simuler le fonctionnement du "sonar" en envoyant des impulsions à 40kHz via un émetteur et les recevoir via un récepteur;

Nous devons donc réfléchir à la conception d'une partie FPGA et d'une partie analogique :

- La partie FPGA nous permettra d'envoyer des trains d'impulsions à 40KHz, qui une fois amplifiée, seront connectées à l'émetteur piézoélectrique

- La partie analogique nous permettra d'amplifier et de de renvoyer les signaux reçus à la partie FPGA

A la fin de cette première séance nous devrons au moins terminer de configurer les différents compteurs et portes logiques de la partie d'émission, et réfléchir à la partie de réception

Partie informatique

Comprendre les objectifs, installer les bibliothèques nécessaires (prototype, phildget etc...), découvrir et utiliser le matériel, Coder en C des premiers programmes nécessaires. Etudier l'utilisation de javascript ( a l'aide du wiki par exemple) et comprendre le site php à realiser.

Bilan séance 1

Partie informatique

Projet compris, étude des exemples fournies pour controler le Servo-moteur, création d'un programme de pilotage par position, reflexion pour balayage. Compréhension faite de la bibliothèque prototype, début de rédaction des pages html nécessaires (avec appel du programme en C et du programme php)

Partie électronique

Le sujet est compris dans son ensemble; la plupart des difficultés du système à concevoir ont été identifiés.

Les différents amplificateurs nécessaires pour la partie analogique sont définis.

Nous avons réfléchi au sujet et commencé à écrire des schémas concernant la conception de notre système.

Puis nous avons implantés la partie d'émission du FPGA sur Altium, pour l'instant il n'y a pas d'erreur de compilation.

Objectif séance 2

Partie électronique

Après une semaine de réflexion suite à notre premier système, nous devons mettre en place des améliorations:

=> un moyen technique permettant d'arrêter le compteur lorsque le signal de retour est détecté

=> relier les deux compteurs à la même horloge afin de les réinitialiser en même temps

=> mettre une porte ET entre le circuit de l'émetteur et du récepteur afin que le récepteur ne fonctionne pas quand on emet nos impulsions

=> Effectuer un schéma électrique de la partie analogique afin de faciliter le câblage

=> réaliser la partie réception du FPGA sur Altium

Partie informatique

Le but de cette séance est de communiquer entre la plateforme phidget et le sonar (utilisation de requete AJAX aidée par la bibliothèque Prototype). Realisation de modification de l'orientation a partir du site, puis récupération de la distance.

Bilan séance 2

Partie électronique

Voici le bilan de cette séance

=> nous utiliserons une horloge de période 1 seconde, ce sera notre temps de référence pour la mise à jour des données du sonar

=> Les modifications concernant le fichier Altium ont été effectuées; le câblage a été optimisé (voir le bilan de la dernière séance)

=> Les ébauches des câblages de la partie analogique ont été montré et validé par l'équipe pédagogique

Partie informatique

Les fichiers html pour le site sont faits, les fichiers en C et php communiquant avec la plateforme phidget sont réalisés, une phase de débuggage est nécessaire en début de séance suivante.

Objectifs de la séance 3

Partie électronique

Pour cette séance nous devrons impérativement :

=> câbler le circuit de la partie analogique

=> Terminer les parties d'émission et de réception du FPGA et observer les impulsions sur l'analyseur logique

=> Relier les parties FPGA et analogiques

Partie informatique

Le but de cette dernière séance est de faire fonctionner le site correctement( en réalisant un debuggage), c'est à dire avoir l'émission d'une orientation et la réception de la distance obtenue par le sonar (affichée sur le site) . Enfin l'implémentation sur la foxboard doit être réalisée.

Bilan séance 3

Partie électronique

Voici le bilan de cette séance :

=> Le câblage du circuit partie analogique du sonar a été réalisé

=> Les parties d'émission et de réception du FPGA sont terminées

=> Hélas nous n'avons pas pu relier les parties FPGA et analogiques car nous ne savions pas que les boutons de la nanoboard ont par défaut

leurs interrupteurs en position fermées. Il a donc fallu changer la configuration de l'implantation sur Altium, et lors de la compilation

nous avons utilisé "plus de 100%" de la capacité du logiciel, et nous n'avons donc pas eu le temps de modifier notre projet...

Partie informatique

en cours de rédaction

Partie informatique

Partie électronique

Partie FPGA

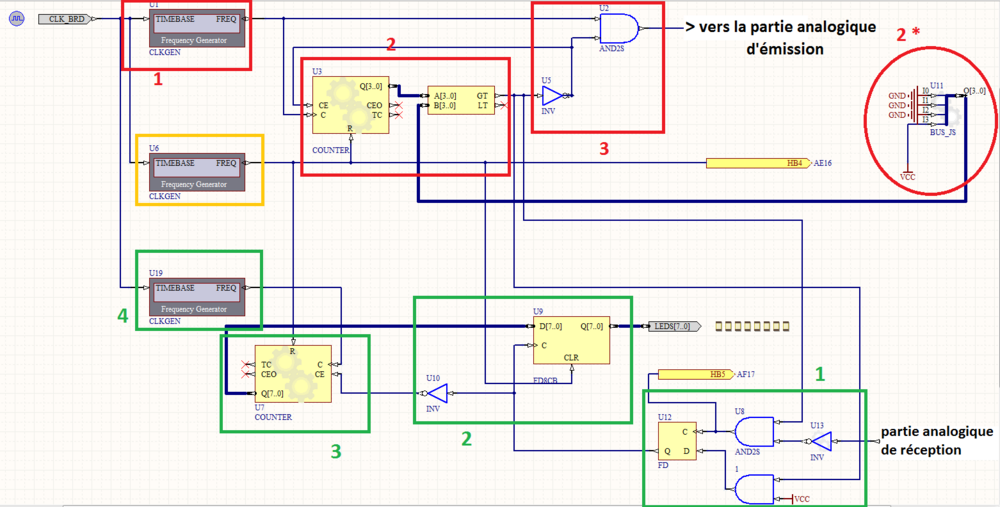

Partie d'émission (en rouge)

Le bloc 1 émet une fréquence de 40 Khz, qui correspond à la fréquence qui permet au piezo d'envoyer des ultrasons.

Le bloc 2 permet de compter le nombre d'impulsion envoyé, et cette valeur est comparée au bloc 2*, ici la valeur choisir est de 8 impulsions. Dès que le nombre d'impulsions calculées est de 8, ce bloc nous renvoit du 1 logique.

Dans le bloc 3 ce 1 logique est transformé en 0 logique par une porte NON, et nous envoyons ce 0 logiques dans le compteur CE afin de le stoper, mais aussi dans une porte ET où est reliée l'émission des impulsions de 40KHz, ce qui nous permet, après les 8 impulsions émises, d'arrêt d'émettre. Et ce, afin de ne pas perturber la partie de réception lorsqu'elle attendra les signaux de retours du sonar.

Sur l'image ci-dessus vous pouvez observer le résultat de la partie d'émission : l'envoi périodique de 8 impulsions de fréquence 40 Khz.

Partie de réception (en vert)

Le bloc 4 permet d'envoyer des impulsions à une certaine fréquence, dont dépend la précision (expliqué dans une autre partie), au compteur du bloc 3, ce qui permet de compter le temps écoulé, de l'émission à la réception du sonar.

Le bloc 1 permet, dès que la partie analogique de réception reçoit un signal de retour et alimente l'horloge de la bascule D, d'envoyer soit du 1 logique (+VCC), si le bloc 2 rouge donne du 1 logique (ie : nous avons envoyé nos 8 impulsions), soit du 0 logique si le bloc 2 rouge nous donne du 0 logique (ie : nous n'avons pas terminé d'envoyer nos 8 impulsions).

Dès que le bloc 2 reçoit du 1 logique dans son horloge (C), il transmet la valeur que le compteur du bloc 3 lui envoit, à la sortie de son registre qui est reliée à la partie informatique du projet. Puis la porte inverseuse permet d'envoyer du 0 logique au "Counter Enable" (CE), ce qui permet de stopper le compteur.

Quant au bloc jaune, il a pour but de remettre à zéro tous les compteurs, en même temps, à chaque seconde.

Partie analogique

Schéma du câblage

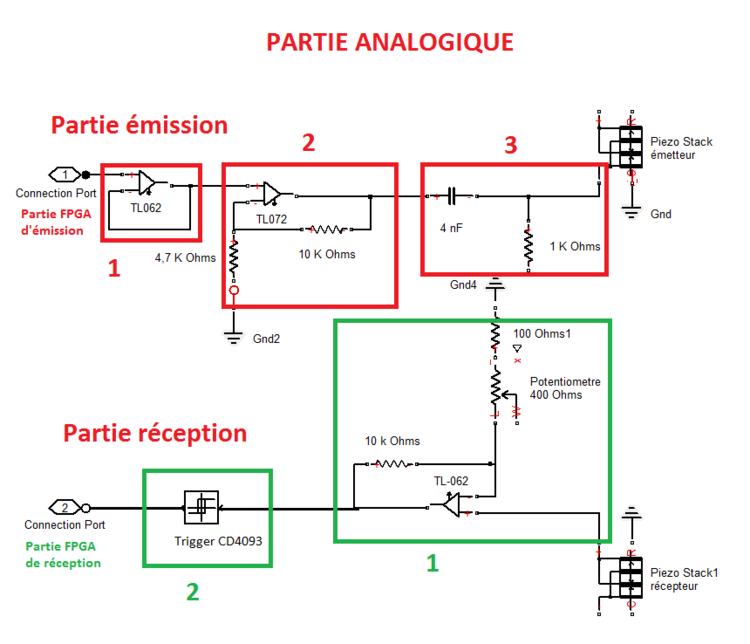

Partie d'émission (en rouge)

Le bloc 1 de la partie d'émission est composé d'un AOP de type TL062, il est configuré en suiveur, son rôle est de protéger la nanoboard.

Puisque la partie FPGA ne nous délivre que du 0-5V, et pour augmenter la puissance du signal, le bloc 2 comporte un AOP de type TL072 avec un gain de 3 (grâce aux deux résistances de 4.7k Ohms et 10k Ohms), nous obtenons donc à sa sortie du 0-15V.

Le bloc 3 a pour but de nous sélectionner que la gamme de fréquence qui nous interesse : aux alentours de 40k Hz. Il est ensuite relié à l'émetteur.

Partie de réception (en vert)

Juste après le récepteur, le bloc 1 a pour rôle d'amplifier le signal reçu, c'est pour cela qu'il a un gain de 20. C'est nécessaire puisque le signal de retour n'est que de quelques millivolts.

Le bloc 2 contient un Trigger CD4093, il a pour but de nous renvoyer du +5V, soit du 1 logique pour la partie de réception du FPGA, dès qu'il reçoit un signal de retour (qui n'est pas un signal parasite).

Câblage du sonar

1 : Il s'agit de l'émetteur piézoélectrique.

2 : Le récepteur piézoélectrique.

3 : Le Trigger4093.

4,5,6 : Ce sont les 3 AOP décrit plus haut.

7 : Il s'agit du filtre : condensateur + résistance nous permettant de sélectionner la gamme de fréquence aux alentours de 40k Hz.

8 : vous pouvez observer dans le cadre bleu les alimentations; la première ligne est le potentiel +15V, la deuxième ligne est le potentiel 0V, puis grâce au régulateur situé en 8, nous avons une alimentation +5V à partir de l'alim +15V.

Fonctionnement

Nous avons deux modes de fonctionnement :

=> Mode distance "approximative"

Ce mode correspond a une résolution de 64,79 cm et détecte sur 164m

Configuration :

Fréquence du bloc 1 rouge à 40k Hz, Fréquence du bloc jaune à 1Hz, Fréquence du bloc 4 vert à 263 Hz.

=> Mode distance "précise"

Ce mode de fonctionnement a une résolution de 7,84 mm, mais ne détecte que sur 2m.

Configuration :

Fréquence du bloc 1 rouge à 40k Hz, Fréquence du bloc jaune à 1Hz, Fréquence du bloc 4 vert à 21,74k Hz.

Les calculs ont été réalisé en se basant sur la vitesse du son (341 m/s)

A noter que si le système renvoit la valeur 255, cela signifie qu'aucun obstacle n'a été détecté par le sonar.