Contrôle de sonar, 2011/2012, TD2

Sommaire

Evaluation informatique et électronique

Gestion de projet / rédaction Wiki

Note .

Test fonctionnels

- Sous-système :

- Système :

Qualité de la réalisation

- Informatique. Note %.

- procédure de test :

- pages HTML et Javascript :

- scripts PHP ou programmes C :

- installation sur FoxBoard :

- Electronique : Note %.

- qualité de la réalisation :

- tests autonomes :

Bilan

Tous les points principaux ont un poids équivalent (sauf "système" qui est un bonus).

Note finale :

Présentation

Projet Sonar

Objectif principal :

Le but de notre projet est de réaliser un sonar qui transmet des trains d'ondes à 40Khz et qui les reçoit à l'aide de capteurs ultrasons pour traduire une information qui sera traitée par la NanoBoard (calcul de la distance entre lui et un objet par exemple). Pour communiquer avec ce sonar par le protocole série, nous utiliserons la FoxBoard qui permet d'afficher sous forme d'une image l'environnement détecté par le sonar.

Objectif et bilan des séances :

Objectif de la séance n°1 :

Dans cette première séance, nous avons essayé de bien assimiler le sujet pour éviter les lacunes et pour avancer progressivement dans notre travail . Puis, nous nous sommes donnés des rôles afin qu'on puisse mieux avancer et mieux s'organiser. Pour la partie électronique, nous devons générer des trains d'ondes à la fréquence de 40KHz et les amplifier pour ne pas les perdre. Ces trains d'onde vont parcourir 4m aller retour.

Bilan de la séance n°1 :

Partie électronique :

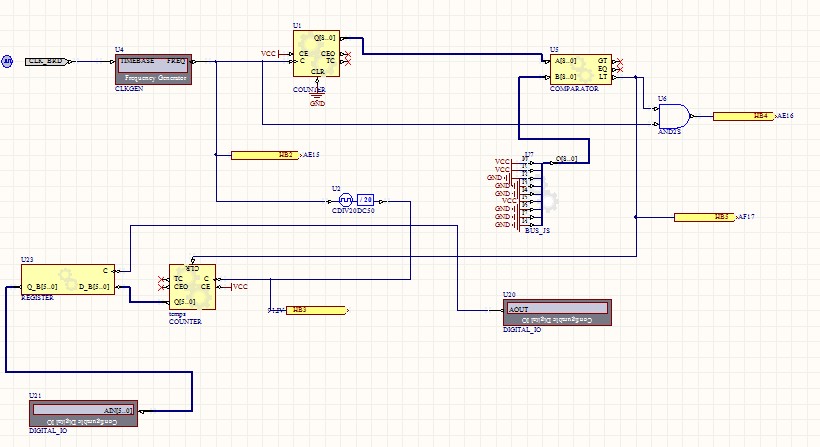

Nous avons réussi à implanter la partie d'émission du FPGA sur Altium en utilisant un signal carré à la fréquence de résonance, un compteur 6 bits et un comparateur qui permet d'arrêter le compteur, donc d'annuler les fronts montants, et c'est ce qui va donner des trains d'ondes. Pour la partie analogique, nous avons fait théoriquement un montage (Amplificateur et résistances) qui nous permettra d'amplifier le signal transmis d'un gain de 3.

Partie informatique :

Objectif de la séance n°2 :

Dans cette deuxième séance, nous devons réaliser la partie de réception qui consiste à recevoir les trains d'ondes et à les ré-amplifier puisqu'ils sont légèrement modifiés et bruités par le trajet.

Bilan de la séance n°2 :

Partie électronique :

Nous avons réussi à implanter la partie de réception du FPGA sur Altium en simulant le retour des trains d'ondes (Configure Digital) et en utilisant un deuxième compteur (pour calculer la durée entre l'émission et la réception des trains d'ondes). Et pour stopper ce 2ème compteur, on l'a relié avec le comparateur de la partie d'émission puisque quand LT se met à 1, le 2ème compteur s'arrête et s'initialise à 0 (CLR=1). En outre, on utilise le diviseur de fréquence(CDIV20DC50) pour que les trains d'onde aient suffisamment de temps pour parcourir 4m avant que le second compteur n'atteigne sa valeur maximale. Pour la partie analogique, nous avons réalisé théoriquement un montage qui permettra d'amplifier le signal reçu d'un gain de 30 puisque le signal de retour n'est que de quelques millivolts.

Partie informatique :

Objectif de la séance n°3 :

L'objectif de cette troisième séance est de pouvoir mémoriser les données par le 2ème compteur qui calcule la durée entre l'émission et la réception du signal. Il faut aussi terminer la partie analogique qui servira à amplifier le signal transmis et reçu.

Bilan de la séance n°3 :

Partie électronique :

Quand on aura un front montant (c'est-à-dire quand le capteur ultrason détectera les trains d'onde),

la bascule D va mémoriser les données de 6 bits. Puis, le 2ème compteur se remettra en marche une nouvelle fois puisqu'au moment où le signal sera reçu, un nouveau signal va être généré.

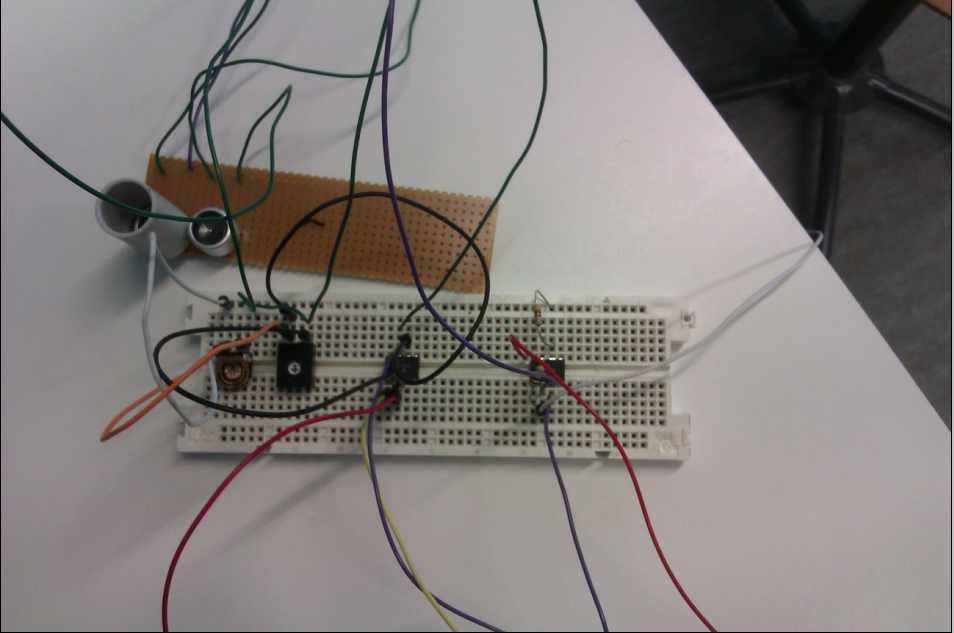

Pour la partie analogique, on a fait le câblage nécessaire qui permettra d'amplifier les trains d'ondes lors de l'émission et de la réception.

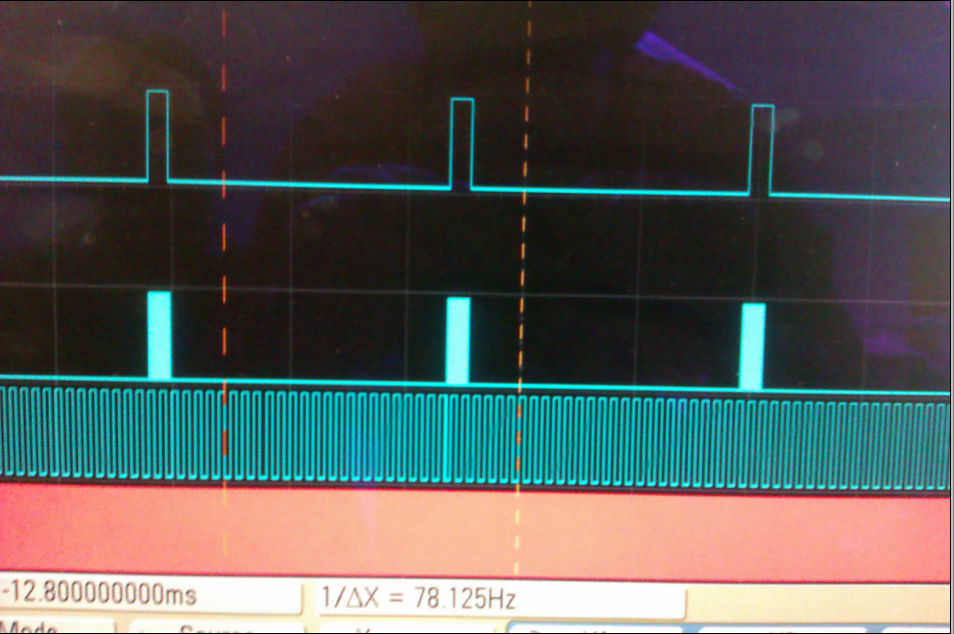

De haut en bas :

-Le premier tracée représente l'initialisation du 2ème compteur.

-Le second tracée représente les trains d'ondes émis.

-Le troisième tracée représente le diviseur de fréquence utilisé par le deuxième compteur.

-Le dernier tracée représente la fréquence de l'entrée du système (CLK : l'horloge).

Partie informatique :

Schéma final de la partie électronique :